# **PSØ81**

Single Chip Solution for Strain Gauges

July 4th, 2012

Document-No.: DB\_PSØ81\_en VO.9

Published by acam-messelectronic gmbh

© acam-messelectronic gmbh 2012

## **Disclaimer / Notes**

The information provided by this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by acam for its use, nor for any infringements of patents or other rights of third parties that may result from its use. The information is subject to change without notice and is provided "as is" without warranty of any kind (expressed or implied). Picostrain is a registered trademark of acam. All other brand and product names in this document are trademarks or service marks of their respective owners.

#### Support

For a complete listing of Direct Sales, Distributor and Sales Representative contacts, visit the acam web site at: http://www.acam.de/company/distributors or refer to chapter 7.2 in this datasheet

For technical support you can contact the acam support team in the headquarter in Germany or the Distributor in your country. The contact details of acam in Germany are: support@acam.de or by phone +49-7244-74190.

| 1 Overview  2 Characteristics and Specifications  3.1 Overview  3.2 Measurement Principle | 1-2<br>2-2    |

|-------------------------------------------------------------------------------------------|---------------|

| 3.1 Overview 3.2 Measurement Principle                                                    | 2-2           |

| 3.2 Measurement Principle                                                                 |               |

|                                                                                           | 3-2           |

|                                                                                           | e <b>3</b> -2 |

| 3.3 Converter Front End 3.3 Connecting the Strain                                         | Gauges 3-3    |

| 3.4 Capacitor, Cycle Time,                                                                | 3-10          |

| 3.5 Modes and Timings                                                                     | 3-15          |

| 3.6 Post-processing                                                                       | 3-25          |

| 4.1 Oscillators                                                                           | 4-2           |

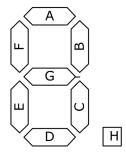

| 4.2 LCD-Driver 4.2 LCD-Driver                                                             | 4-3           |

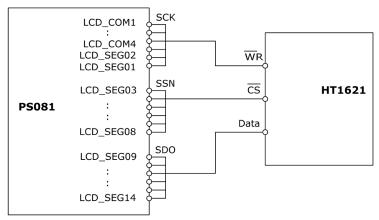

| & Special Settings 4.3 Support of an External                                             | LCD 4-14      |

| 4.4 I/O-pins                                                                              | 4-16          |

| 4.5 SPI-Interface                                                                         | 4-19          |

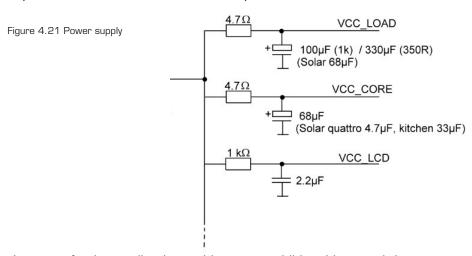

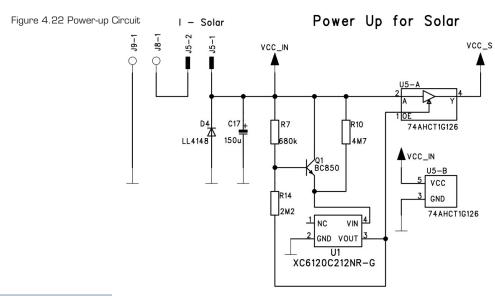

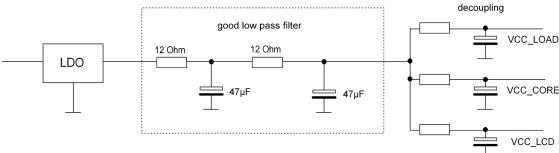

| 4.6 Power Supply                                                                          | 4-26          |

| 5 Configuration Registers                                                                 | 5-2           |

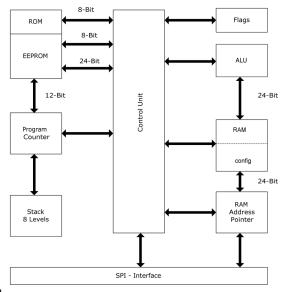

| 6.1 Block Diagram                                                                         | 6-2           |

| 6.2 Memory Organization                                                                   | 6-2           |

| 6 Central Processing Unit 6.3 Status and Result Reg                                       | isters 6-5    |

| (CPU) 6.4 Instruction Set                                                                 | 6-8           |

| 6.5 System Reset, Sleep N                                                                 | /lode 6-34    |

| 7.1 Migration from PS08                                                                   | 7-            |

| 7.2 Bug Report                                                                            | 7-3           |

| 7.3 Known issues and solu                                                                 | tions 7-4     |

| 7.4 Literature Guide                                                                      | 7-4           |

| 7.5 Document History                                                                      | 7-5           |

| 8 Appendix                                                                                | 8-2           |

# **Table of Contents**

# Page

| 1   | Overview                 | 1-2 |

|-----|--------------------------|-----|

| 1.1 | Features                 | 1-2 |

| 1.2 | Advantages               | 1-2 |

| 1.3 | Applications             | 1-2 |

| 1.4 | General Description      | 1-2 |

| 1.5 | Functional Block Diagram | 1-3 |

# 1 Overview

#### 1.1 Features

- RMS noise:

- 20.1nV fast settle, 5 Hz

- 11.5 nV SINC3, 5 Hz

- 8.9 nV SINC5, 5 Hz

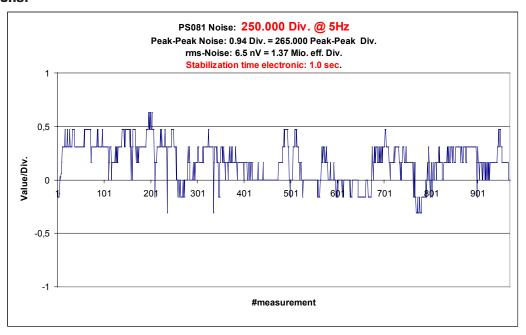

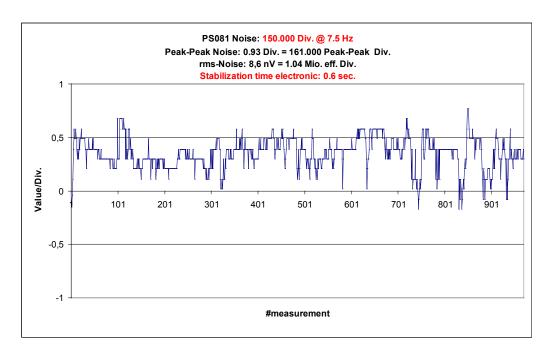

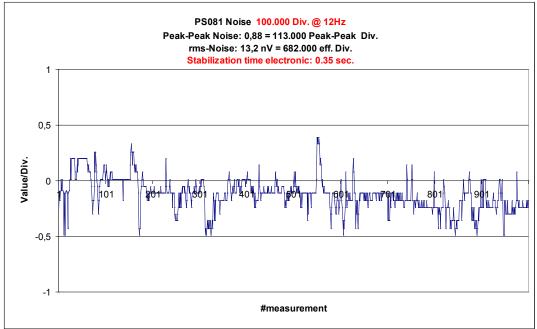

- Up to 250,000 peak-peak divisions in weighing applications (2 mV/V strain)

- Scalable udapte rate from < 1 Hz to 1000 Hz

- Current consumption:

- ~ 0.39 mA PSØ81 itself (at maximum speed)

- ~ 0.005 mA PSØ81 itself (at low current configuration)

- ~ 0.001 mA standby current

- Power supply voltage: 2.1 V to 3.6 V

- Converter type: Time-to-digital converter (TDC)

- Resolution: 28 bit ENOB (RMS) or 25.8 bit noise-free (peak-to-peak)

- 24-Bit internal microprocessor with 2 KB reprogrammable EEPROM

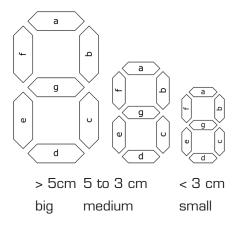

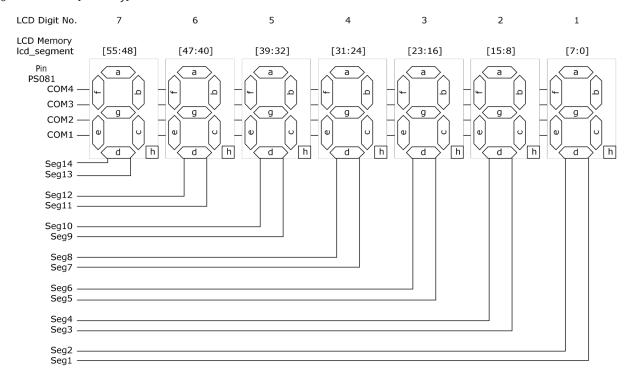

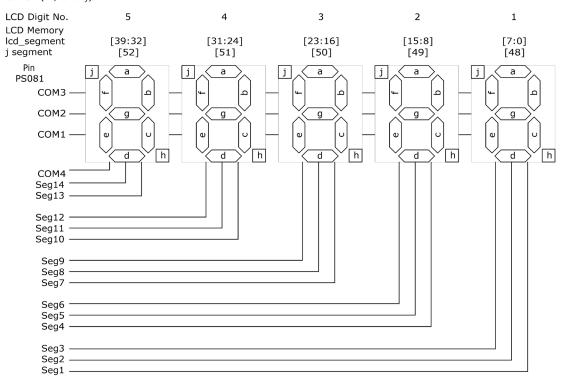

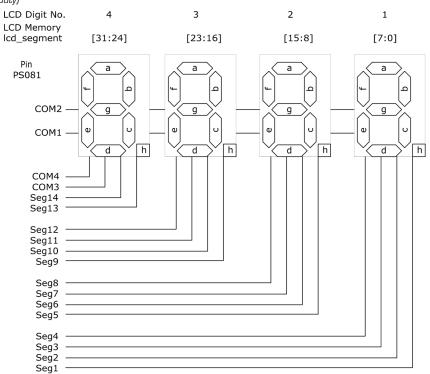

- Internal LCD controller for 4x14, 3x15 and 2x16 segments

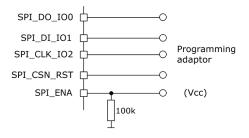

- 4-wire serial SPI interface

- Internal very low current 10 kHz oscillator

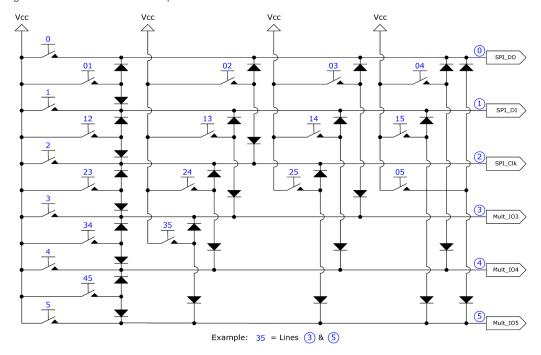

- 6 I/O pins, configurable up to 21 inputs or 5 outputs

- Very high power supply rejection ratio (PSRR)

- Very low gain and offset drift

- Embedded charge pump for driving the LCD

- Embedded bandgap voltage reference for low battery detection

- Watchdog timer

# 1.2 Advantages

- Single-chip solution for weighing applications

- Converter, microcontroller and LCD controller in one chip

- Extreme low total system current (down to 15µA including strain gages)

- Very low self heating of teh sensor

- Gain and offset correction of the load cell

- Available as dice (115 µm pitch) or packaged (QFN56, 7x7 mm²)

# 1.3 Applications

#### Industrial

- Torque wrenches

- Pressure indicators

- Legal for trade scales

- Counting scales

#### Consumer

- Pure solar driven scales

- Body scales

- Kitchen scales

- Pocket scales

- Hanging scales

- Postal scales

- Package scales

#### 1.4 General Description

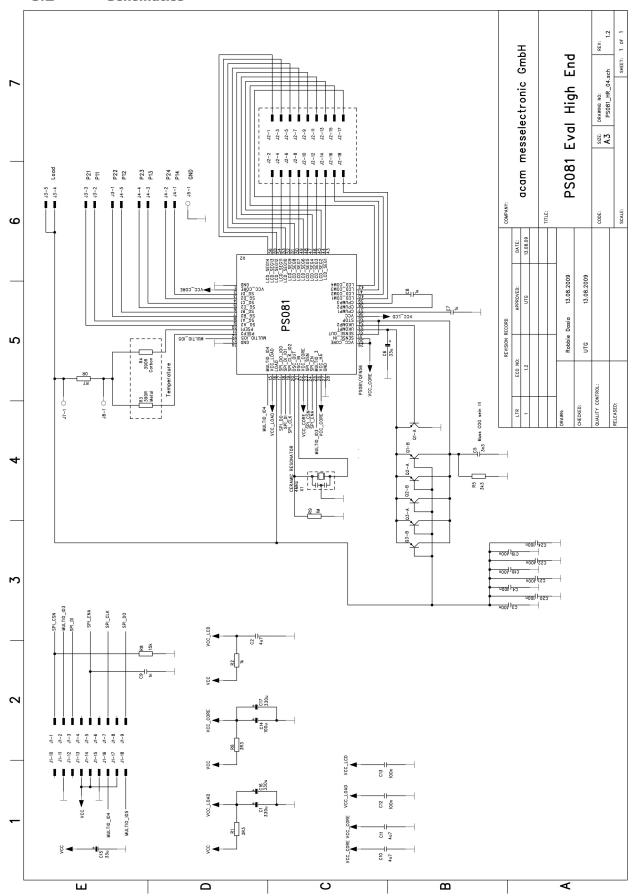

The PSØ81 is a system-on-chip for ultra low-power and high resolution applications. It was designed especially for weight scales but fits also to any kind of force or torque measurements based on metal strain gages. It takes full advantage of the digital measuring principle of PICOS-TRAIN. Thus, it combines the performance of a 28-Bit signal converter with a 24-Bit microprocessor. Additional elements like an LCD driver, 3K ROM with many complex pre-defined functions,

2K EEPROM program memory and an integrated 10 kHz oscillator round off the device. A small amount of external components is sufficient to build a complete weighing electronic.

The part operates with a power supply from 2.1V to 3.6V and has a very low current consumption. As per configuration the current consumption ranges between 0.005 mA and 0.4 mA approximately. The update rate is scalable in a wide range from < 1 Hz up to 1000 Hz. With a maximum of mor then 1 million internal divisons (28 bit ENOB RMS) the resolution lies in the top range of today's converters. This high resolution is only comparable to the one of high-end AD converters, but at a much lower current consumption. Equipped with these features, a variety of scale electronics can be served with PSØ81. On the resolution side, it allows to build scales with up to

250,000 stable peak-peak divisons (at 2mV/V)! On the other hand, a sophisticiated power management and the special features of the PICOS-TRAIN measuring principle can reduce the total current of the system down to 15  $\mu$ A, including the sensor current. This way, it is the first time possible to build pure solar driven weigh scales based on metal strain gages. Of course, the benefits can be combined, e.g. building a high resolution scale with a low current such as a legal for trade scale that runs more than 1,500 operating hours with 2x AA batteries.

Throwing a glance at further features like software adjustment of the offset and gain compensation or the possibility to operate only one half bridge reveals that the PSØ81 opens the door to new and innovative product solutions.

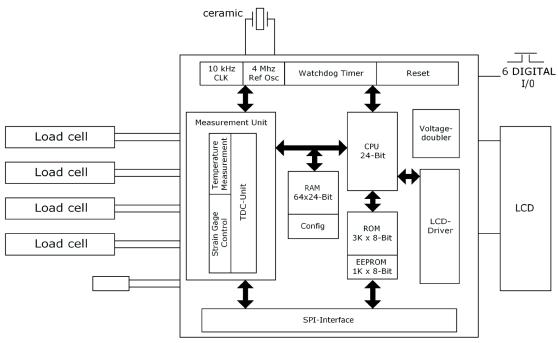

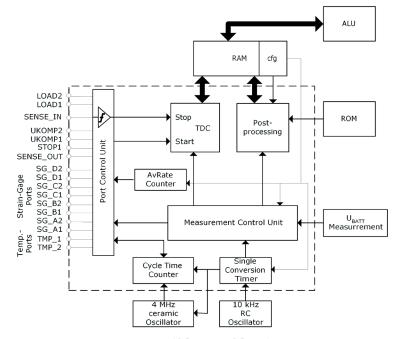

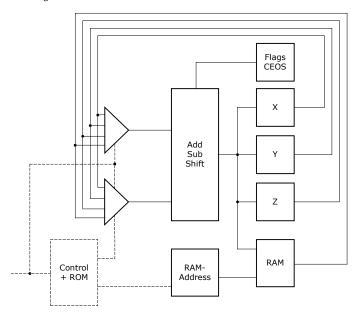

# 1.5 Functional Block Diagram

Figure 1.1 Block Diagram

# Table of Contents

# **P**age

| 2   | Characteristics and Specifications | 2-2 |

|-----|------------------------------------|-----|

| 2.1 | Absolute Maximum Ratings           | 2-2 |

| 2.2 | Normal Operating Conditions        | 2-2 |

| 2.3 | Electrical Characterization        | 2-2 |

| 2.4 | Converter Precision                | 2-3 |

| 2.5 | Integral Nonlinearity              | 2-4 |

| 2.6 | Resolution vs. Supply Voltage      | 2-6 |

| 2.7 | Current Consumption                | 2-7 |

| 2.8 | Timings                            | 2-7 |

|     | Pin Assignment                     |     |

# 2 Characteristics and Specifications

# 2.1 Absolute Maximum Ratings

Table 2.1 Maximum Ratings

| Symbol Parameter         |                      | Conditions      | Min  | Max       | Unit |

|--------------------------|----------------------|-----------------|------|-----------|------|

| Vcc                      | Supply voltage       | Vcc vs. GND     | -0.5 | 5.0       | V    |

| Vcc_load                 |                      |                 |      |           |      |

| Vcc_osc                  |                      |                 |      |           |      |

| Vcc_LCD                  |                      |                 |      |           |      |

| Vin                      | Vin DC input voltage |                 | -0.5 | Vcc + 0.5 | V    |

| ESD Rating               | FICDM                | All pins        | 2    |           | kV   |

| Tstg Storage Temperature |                      | Plastic package | -55  | 150       | °C   |

# 2.2 Normal Operating Conditions

Table 2.2 Operating Conditions

| Symbol   | Parameter             | Conditions                     | Min    | Max   | Unit |

|----------|-----------------------|--------------------------------|--------|-------|------|

| Vcc      | Supply voltage        | Vcc vs. GND                    | 2.1    | 3.6** | V    |

| Vcc_load |                       |                                | (1.5*) |       |      |

| Vcc_osc  |                       | (* without EEPROM programming, |        |       |      |

| Vcc_LCD  |                       | voltage measurement and LCD)   |        |       |      |

| Vin      | DC input voltage      |                                | 0.0    | Vcc   | V    |

| Vout     | Output voltage        |                                | 0.0    | Vdd   | V    |

| Тор      | Operating temperature |                                | -40    | 125   | °C   |

| Tstg     | Storage temperature   | Plastic package                | -55    | 150   | °C   |

<sup>\*\* 4.5</sup> V for highest resolution within limited temperature range

# 2.3 Electrical Characterization

Table 2.3 Electrical Characterization

| Symbol             | Parameter                                | Conditions                                                              | Min    | Тур.                           | Max    | Unit |

|--------------------|------------------------------------------|-------------------------------------------------------------------------|--------|--------------------------------|--------|------|

| Vil                | Input low voltage                        | CMOS                                                                    |        |                                | O.3Vcc | V    |

| Vih                | Input high voltage                       | CMOS                                                                    | 0.7Vcc |                                |        |      |

| Vhyst              | Input hysteresis                         | Vcc = 3.6 V<br>Vcc = 3.0 V<br>Vcc = 2.7 V<br>Vcc = 2.2 V<br>Vcc = 1.8 V |        | 400<br>280<br>225<br>150<br>80 |        | mV   |

| Voh                | Output high voltage                      |                                                                         | 0.8    |                                |        | V    |

| Vol                | Output low voltage                       |                                                                         |        |                                | 0.2Vcc | V    |

| Vlbat              | Low battery voltage detect               |                                                                         | 2.2    |                                | 2.9    | V    |

| LCD_COM<br>LCD_SEG | LCD driver Voltage stabilized            | lcd_vlt = 0<br>  lcd_vlt = 1<br>  lcd_vlt = 2                           |        | 2.0<br>2.5<br>3.0              |        | V    |

| lq                 | Quiescent current                        | No oscillator, no TDC                                                   |        | 150                            |        | nA   |

| losc               | Current 4 MHz oscillator continuously on | Vcc = 3.6 V<br>Vcc = 3.0 V<br>Vcc = 2.1 V                               |        | 200<br>130<br>65               |        | μΑ   |

#### 2.4 Converter Precision

Table 2.4 Performance at Vcc = 3.3V with **external** comparator

|           | ENOB dR/R strain resistance |       |       |  |  |  |

|-----------|-----------------------------|-------|-------|--|--|--|

| Frequency | No filter                   | SINC3 | SINC5 |  |  |  |

| (Hz)      |                             |       |       |  |  |  |

| 500       | 23.8                        | 24.8  | 25.2  |  |  |  |

| 250       | 24.4                        | 25.2  | 25.7  |  |  |  |

| 100       | 25.2                        | 25.8  | 26.1  |  |  |  |

| 50        | 25.5                        | 26.2  | 26.5  |  |  |  |

| 20        | 26.0                        | 26.8  | 27.0  |  |  |  |

| 10        | 26.6                        | 27.4  | 27.7  |  |  |  |

| 5         | 27.2                        | 27.9  | 28.3  |  |  |  |

Table 2.5 Performance at Vcc = 3.3V with external comparator, related to 2 mV/V strain (weigh scale)

|           | Resolution @ 2 mV/V max. out, Fast settle * |           |          |           |  |  |  |

|-----------|---------------------------------------------|-----------|----------|-----------|--|--|--|

| Frequency | ENOB                                        | Divisions | Noise nV | Noise nV  |  |  |  |

| (Hz)      |                                             | effective | rms      | peak-peak |  |  |  |

| 500       | 14.8                                        | 28,000    | 231      | 1,386     |  |  |  |

| 250       | 15.4                                        | 44,000    | 148      | 891       |  |  |  |

| 100       | 16.2                                        | 74,000    | 89       | 535       |  |  |  |

| 50        | 16.5                                        | 95,000    | 69       | 416       |  |  |  |

| 20        | 17.0                                        | 133,000   | 49       | 297       |  |  |  |

| 10        | 17.6                                        | 200,000   | 33       | 198       |  |  |  |

| 5         | 18.2                                        | 294,000   | 22       | 135       |  |  |  |

<sup>\*</sup> Fast settle = without filter

Table 2.6 Performance at Vcc = 3.3V with **external** comparator, related to 2mV/V strain (weigh scale) With SINC3 and SINC5 filter (rolling average of 3 respectively 5)

|           |      |           |          |           | Resolu<br><i>Filter</i> | tion @ <i>2 m</i> l | <b>//V</b> max. o | ut, <i>SINC5</i> |

|-----------|------|-----------|----------|-----------|-------------------------|---------------------|-------------------|------------------|

| Frequency | ENOB | Divisions | Noise nV | Noise nV  | ENOB                    | Divisions           | Noise nV          | Noise nV         |

| (Hz)      |      | effective | rms      | peak-peak |                         | effective           | rms               | peak-peak        |

| 500       | 15.8 | 55,000    | 118      | 713       | 16.2                    | 74,000              | 89                | 535              |

| 250       | 16.2 | 74,000    | 89       | 535       | 16.7                    | 105,000             | 62                | 376              |

| 100       | 16.8 | 114,000   | 57       | 347       | 17.1                    | 142,000             | 46                | 277              |

| 50        | 17.2 | 153,000   | 42       | 257       | 17.5                    | 181,000             | 36                | 218              |

| 20        | 17.8 | 222,000   | 29       | 178       | 18.0                    | 266,000             | 24                | 149              |

| 10        | 18.4 | 344,000   | 19       | 115       | 18.7                    | 416,000             | 15                | 95               |

| 5         | 18.9 | 476,000   | 13       | 83        | 19.3                    | 625,000             | 10                | 63               |

Table 2.7 Performance at Vcc = 3.3V with **internal** comparator

|           | ENOB dR/R | strain resis | stance | ENOB 2mV/V, Fast settle* |

|-----------|-----------|--------------|--------|--------------------------|

| Frequency | No filter | SINC3        | SINC5  |                          |

| (Hz)      |           |              |        |                          |

| 500       | 23.0      | 24.0         | 24.4   | 14.0                     |

| 250       | 23.6      | 24.4         | 25.1   | 14.6                     |

| 100       | 24.4      | 25.0         | 25.3   | 15.4                     |

| 50        | 24.7      | 25.4         | 25.7   | 15.7                     |

| 20        | 25.2      | 26.0         | 26.2   | 16.2                     |

| 10        | 25.8      | 26.6         | 26.9   | 16.8                     |

| 5         | 26.4      | 27.1         | 27.5   | 17.4                     |

<sup>\*</sup> Fast settle = without filter

Table 2.8 General parameters

| Symbol | Parameter                                 | Conditions                                                                             | Min          | Тур                | Max | Unit                      |

|--------|-------------------------------------------|----------------------------------------------------------------------------------------|--------------|--------------------|-----|---------------------------|

| INL    | Integral Non-linearity                    | Supply Voltage 3.0V to 3.6V                                                            |              | 0.01*              |     | μV/V                      |

|        | Offset drift  Gain drift over -20°C +70°C | Total system, 350 $\Omega$ SG Full-bridge Wheatstone Total System. 350 $\Omega$ SG, 5V |              | ± 10<br>< 1<br>~ 1 |     | nV/V/K<br>nV/V/K<br>ppm/K |

| PSSR   | Power Supply Rejection Ratio Vcc          | 1.8V or 3.3 V +-0.3 V                                                                  | 106<br>@1.8V | 130<br>@3.3V       |     | dB                        |

<sup>\*</sup> equals to ± 1.25 ppm of A/D-Converters with PGA setting 128

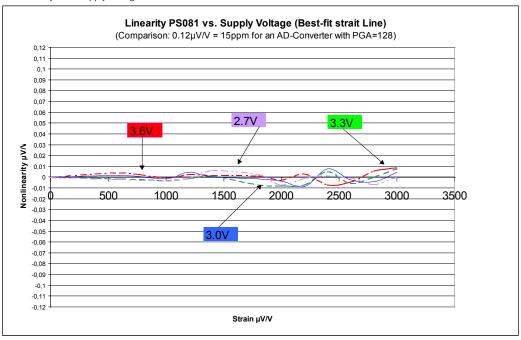

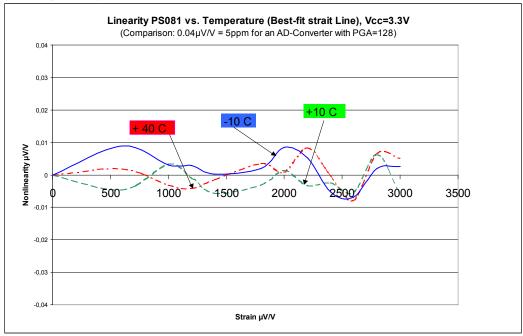

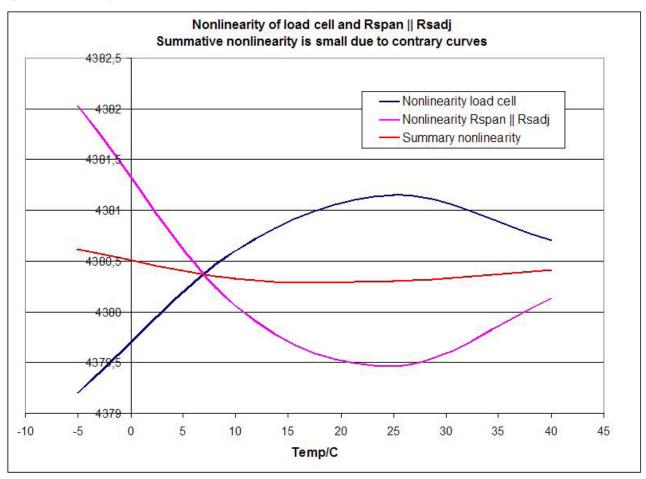

#### 2.5 Integral Nonlinearity

The integral nonlinearity (INL) of PSO81 can be specified to  $\pm$  0.01  $\mu$ V (1.25 ppm). Expressed in divisions this corresponds to  $\pm$  1: 200,000. This is a tremendous high linearity compared to the one of nowadays latest A/D converters. Ordinary A/D converts have a linearity in the range of  $\pm$  0.12 $\mu$ V/V (15 ppm), better A/D converters reach a linearity of  $\pm$  0.4  $\mu$ V (5ppm).

Of course, you can only determine the linearity of the electronics itself, if you can provide a sensor which is accurate and linear enough to measure it. We used for this purpose the revised version of the acam load cell simulator (ALCS350-V2) which offers comfortable methods to investigate not only the linearity, but also variations over temperature or voltage. The linearity of ALCS350-V2 is  $\pm$  0.01  $\mu$ V/V (1:200,000) with PICOSTRAIN wiring and  $\pm$  0.04  $\mu$ V/V with Wheatstone wiring and therefore much more linear than an ordinary load cell. Linearity investigations with the PSO81 and the ALCS350-V2 as a sensor are shown in the following tables. More details about the possibilities and the limitations of the load cell simulator are provided in the ALCS350-V2 datasheet.

<sup>\* \*</sup> using full bridge wiring for minimum zero drift

Figure 2.1 Non-linearity over supply voltage

Figure 2.2 Non-linearity over temperature

#### Note:

Best linearity is achieved with a supply voltage in the range of 3.0 V to 3.6 V. The linearity also depends on the setting for the cycle time. The measurements shown above are done with a cycle time setting of cytime = 85 (equals  $170 \mu s$ ).

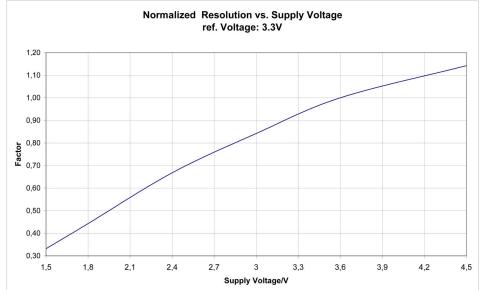

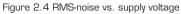

## 2.6 Resolution vs. Supply Voltage

PSØ81 can be driven over a very large supply voltage range. The resolution depends on the supply voltage. The higher the supply voltage the higher the achievable resolution. The diagram below shows the resolution vs. supply voltage which can be achieved with PSØ81. The values refer to 3.0 V. Figure 2.3 Resolution vs. supply voltage

Following diagram shows how the input equivalent noise depends on the supply voltage. The lowest input noise is archived between 2.4 V and 3.6 V. The maximum differential input voltage (e.g. 6.6 mV @ 2mV/V and 3.3 V supply voltage) divided by the input noise gives the effective resolution.

# 2.7 Current Consumption

The following table shows the total system current of the scale (including current through sensor)

Table 2.9 Current consumption at different resolutions

| Divisions * | Update<br>Rate | Double<br>Tara* | Operating Current @ 3V |                  | Scale type                          | Operating hours           |

|-------------|----------------|-----------------|------------------------|------------------|-------------------------------------|---------------------------|

| 2,000       | 3 Hz           | 1<br>mV/V       | 1 kOhm                 | 15 μΑ            | Solar                               |                           |

| 2,000       | 5 Hz           | 1<br>mV/V       | 1 k0hm<br>350 0hm      | 30 μA<br>70 μA   | Postal, Body,<br>Kitchen , Pocket   | 3,000 hours<br>(1xCR2032) |

| 5,000       | 5 Hz           | 1<br>mV/V       | 1 k0hm<br>350 0hm      | 80 μA<br>180 μA  | High-end postal, Kitchen,<br>Pocket | 1,500 hours<br>(1xCR2032) |

| 10,000      | 5 Hz           | 1<br>mV/V       | 1 k0hm<br>350 0hm      | 300 μA<br>700 μA | High-end pocket, Counting           | 2,000 hours<br>(1xCR2430) |

| 80,000      | 5 Hz           | 2<br>mV/V       | 1 kOhm<br>350 Ohm      | 1.9 mA<br>4.5 mA | Counting                            | 1,500hours<br>2 x AA      |

<sup>\*</sup> Divisions are peak-peak values with 5 Sigma (e.g. 80.000 divisions are 400.000 bits of effective resolution)

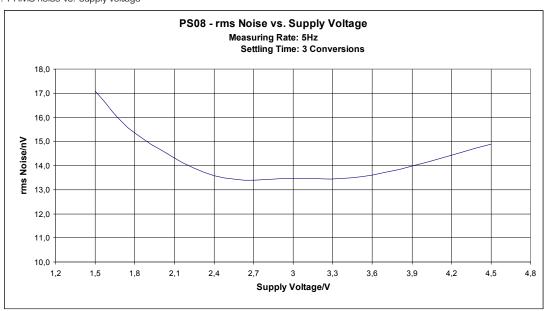

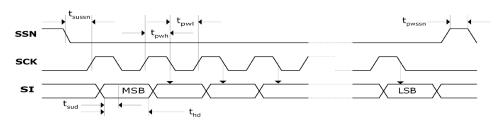

# 2.8 Timings

All timings specified at 3.3V ±0.3V, Ta -40°C to +85°C unless otherwise specified.

Table 2.10 Oscillator timing

| Symbol   | Parameter                                       | Min | Тур | Max | Units |

|----------|-------------------------------------------------|-----|-----|-----|-------|

| Clk10kHz | 10 kHz reference oscillator                     |     | 10  |     | kHz   |

| CIkHS    | High-speed reference oscillator                 |     | 4   |     | MHz   |

| toHSst   | Oscillator start-up time with ceramic resonator |     | 50  | 150 | μs    |

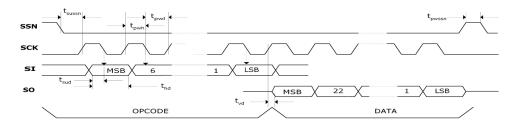

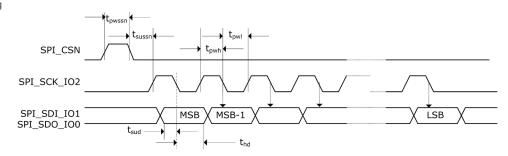

Table 2.11 Serial Interface Timing (SPI)

| Symbol | Parameter                              | Min | Тур | Max | Units |

|--------|----------------------------------------|-----|-----|-----|-------|

| fclk   | Serial clock frequency                 |     |     | 1   | MHz   |

| tpwh   | Serial clock, pulse width high         | 500 |     |     | ns    |

| tpwl   | Serial clock, pulse width low          | 500 |     |     | ns    |

| tsussn | SSN enable to valid latch clock        | 500 |     |     | ns    |

| tpwssn | SSN pulse width between write cycles   | 500 |     |     | ns    |

| thssn  | SSN hold time after SCLK falling       |     |     |     |       |

| tsud   | Data set-up time prior to SCLK falling | 30  |     |     | ns    |

| thd    | Data hold time before SCLK falling     | 30  |     |     | ns    |

| tvd    | Data valid after SCLK rising           |     |     |     | ns    |

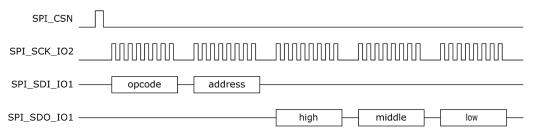

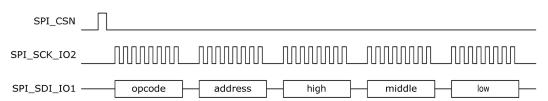

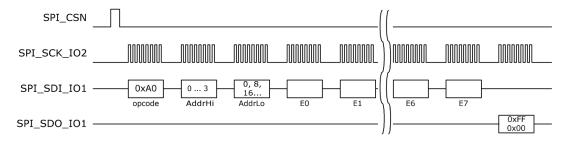

Serial Interface (SPI compatible, Clock Phase Bit = 1, Clock Polarity Bit = 0)

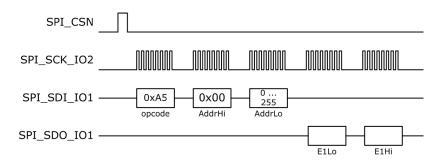

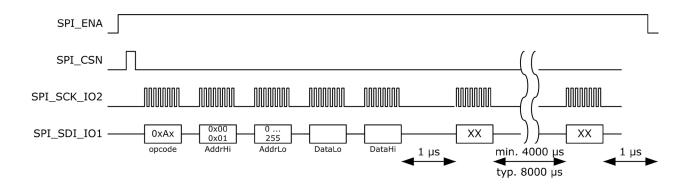

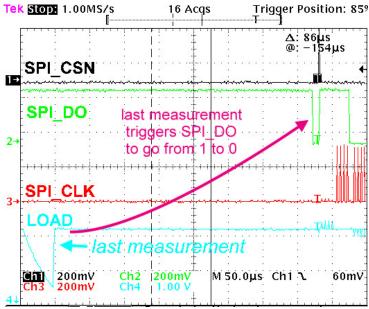

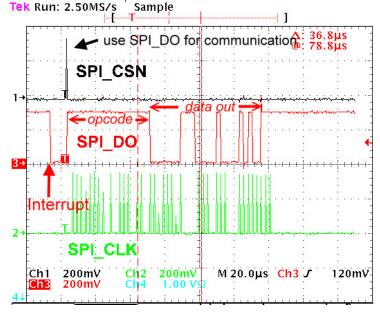

Figure 2.5 SPI - Write access

Figure 2.6 SPI-Read access

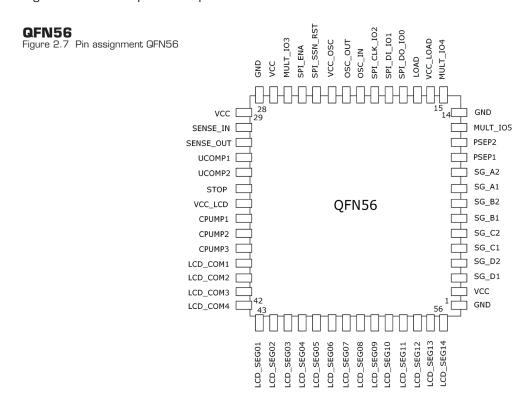

# 2.9 Pin Assignment

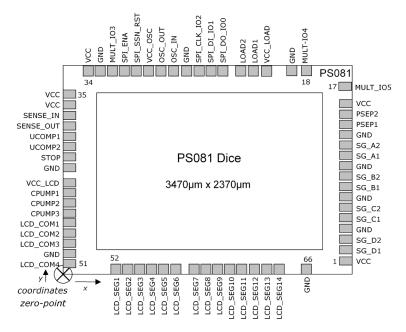

PSØ81 is avaliable as Die or in QFN56 package. The following pictures and tables show the pin assignment and the pin description.

Table 2.12 Pin Description QFN56

| #QFN | Name                       | Description                                                                  | Туре                         |

|------|----------------------------|------------------------------------------------------------------------------|------------------------------|

| 1    | GND                        | Ground                                                                       |                              |

| 2    | Vcc                        | Supply voltage digital part , I/O, 4MHz-osc.                                 |                              |

| 3    | SG_D1                      | Port 1 halfbridge D                                                          | N Open Drain                 |

| 4    | SG_D2                      | Port 2 halfbridge D                                                          | N Open Drain                 |

| 5    | SG_C1                      | Port 1 halfbridge C                                                          | N Open Drain                 |

| 6    | SG_C2                      | Port 2 halfbridge C                                                          | N Open Drain                 |

| 7    | SG_B1                      | Port 1 halfbridge B                                                          | N Open Drain                 |

| 8    | SG_B2                      | Port 2 halfbridge B                                                          | N Open Drain                 |

| 9    | SG_A1                      | Port 1 halfbridge A                                                          | N Open Drain                 |

| 10   | SG_A2                      | Port 2 halfbridge A                                                          | N Open Drain                 |

| 11   | PSEP1                      | Port 1 temperature measurement                                               | N Open Drain                 |

| 12   | PSEP2                      | Port 2 temperature measurement                                               | N Open Drain                 |

| 13   | MULT_I05                   | Multi purpose I/O no. 5                                                      | Mult-IO                      |

| 14   | GND                        | Ground                                                                       |                              |

|      |                            |                                                                              |                              |

| 15   | MULT_I04                   | Multi purpose I/O no. 4                                                      | Mult-IO                      |

| 16   | Vcc_load                   | Power supply load output pin                                                 |                              |

| 17   | Load                       | Load output to measuring capacitor                                           | P Open Drain                 |

| 18   | SPI_D0_I00                 | Output serial SPI interface or IOO                                           | Mult-IO                      |

| 19   | SPI_DI_IO1                 | Input serial SPI interface or IO1                                            | Mult-IO                      |

| 20   | SPI_CLK_IO2                | Clock serial SPI interface or IO2                                            | Mult-IO                      |

| 21   | OSC_IN                     | Input to 4MHz ceramic resonator                                              |                              |

| 22   | OSC_OUT                    | Output to 4MHz ceramic resonator                                             |                              |

| 23   | VCC_OSC                    | 4MHz Oscillator supply voltage                                               |                              |

| 24   | SPI_CSN_RST<br>SPI_SSN_RST | Slave select or RST input (High active)                                      | Input with pull-down         |

| 25   | SPI_ENA                    | Serial SPI interface enable                                                  |                              |

| 26   | MULT_I03                   | Select for Wheatstone comparator MUX or Interrupt or Multi purpose I/O no. 3 | Wheatstone select<br>Mult-IO |

| 27   | Vcc                        | Supply voltage digital part , I/O, 4MHz-osc.                                 |                              |

| 28   | GND                        | GND                                                                          |                              |

|      |                            |                                                                              |                              |

| 29   | Vcc                        | Supply voltage digital part , I/O, 4MHz-osc.                                 |                              |

| 30   | SENSE_IN                   | Input internal CMOS comparator, connect to Vcc if not used                   | Analog In                    |

| 31   | SENSE_OUT                  | Output internal CMOS comparator                                              | Analog Out                   |

| 32   | UCOMP1                     | External comparator circuit connection                                       | Analog Out                   |

| 33   | UCOMP2                     | External comparator circuit connection                                       | Analog Out                   |

| 34   | STOP                       | Stop input measuring signal                                                  |                              |

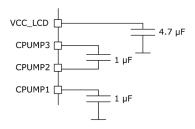

| 35   | VCC_LCD                    | Supply voltage LCD, 10kHz osc., bandgap                                      |                              |

| 36   | CPUMP1                     | LCD voltage doubling and stabilization                                       | Analog Out                   |

| 37   | CPUMP2                     | LCD voltage doubling and stabilization                                       | Analog Out                   |

| 38   | CPUMP3                     | LCD voltage doubling and stabilization                                       | Analog Out                   |

| 39   | LCD_COM1                   | LCD line driver for 1/2, 1/3, 1/4 duty                                       | LCD Buffer                   |

| 40 | LCD_COM2  | LCD line driver for 1/2, 1/3, 1/4 duty                     | LCD Buffer |

|----|-----------|------------------------------------------------------------|------------|

| 41 | LCD_COM3  | LCD line driver for 1/3, 1/4 duty, row driver for 1/2 duty | LCD Buffer |

| 42 | LCD_COM4  | LCD line driver for 1/4 duty, row driver for 1/2, 1/3 duty | LCD Buffer |

| 43 | LCD_SEG1  | LCD row driver                                             | LCD Buffer |

| 44 | LCD_SEG2  | LCD row driver                                             | LCD Buffer |

| 45 | LCD_SEG3  | LCD row driver                                             | LCD Buffer |

| 46 | LCD_SEG4  | LCD row driver                                             | LCD Buffer |

| 47 | LCD_SEG5  | LCD row driver                                             | LCD Buffer |

| 48 | LCD_SEG6  | LCD row driver                                             | LCD Buffer |

| 49 | LCD_SEG7  | LCD row driver                                             | LCD Buffer |

| 50 | LCD_SEG8  | LCD row driver                                             | LCD Buffer |

| 51 | LCD_SEG9  | LCD row driver                                             | LCD Buffer |

| 52 | LCD_SEG10 | LCD row driver                                             | LCD Buffer |

| 53 | LCD_SEG11 | LCD row driver                                             | LCD Buffer |

| 54 | LCD_SEG12 | LCD row driver                                             | LCD Buffer |

| 55 | LCD_SEG13 | LCD row driver                                             | LCD Buffer |

| 56 | LCD_SEG14 | LCD row driver                                             | LCD Buffer |

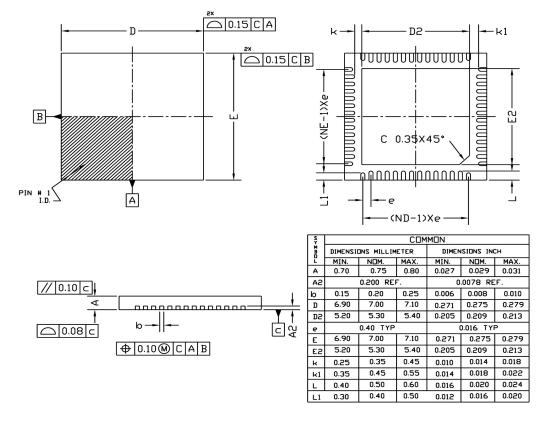

# QFN56 Package Outline

QFN56, 7x7 mm<sup>2</sup>, 0.4mm Pitch

Figure 2.8 Package outline (QFN56)

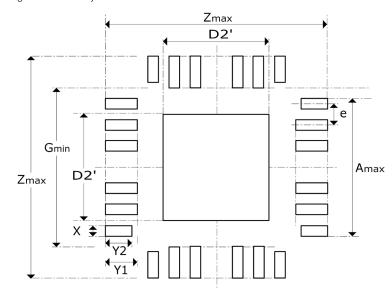

**QFN56** Recommended Pad Layout

|      |   | mm   | inch  |

|------|---|------|-------|

| е    | = | 0.4  | 0.016 |

| Gmin | = | 6.3  | 0.248 |

| Zmax | = | 8.0  | 0.315 |

| D2'  | = | 5.4  | 0.213 |

| Amax | = | 5.45 | 0.215 |

| Χ    | = | 0.25 | 0.010 |

| Y1   | = | 0.85 | 0.033 |

| Y2   | = | 0.75 | 0.030 |

Figure 2.9 Pad Layout

Note: Size of ground plane may not be reduced. It should not contain any vias.

**RoHS:** PSO81FN in QFN56 is RoHS compliant

Material list: Lead frame C194 Cu with PPF finish (NiPdAU)

Die Attach Ablebond 8600, ABlestik

Bond wires Gold

Mold CEL9220HF13H, Hitachi

Marking Laser

Moisture Sensitivity Level 1 (JEDEC J-STD-020,033)

| Reflow Soldering Profile | Average ramp-up rate ( | (TL to Tp) | 3 °C/second max. |

|--------------------------|------------------------|------------|------------------|

|--------------------------|------------------------|------------|------------------|

Preheat

- Temperature Min (TSmin) 140 °C - Temperature Max (TSmax) 200 °C

- Time (min to max) ts 60 - 120 seconds

Tsmax to TL

- Ramp-up rate 3 °C/second max.

Time maintained above:

- Temperature (TL) 220 °C - time (tL) 30 seconds Peak Temperature (Tp) 245 +0 -5 °C Time within 5°C of actual Peak 10 seconds

#### Die

Figure 2.10 Pad assignment Die

Table 2.13 Pad assignment and location Die

| #Pad  | Name       | Description                                  | Туре         | X-Pos<br>Center | Y-Pos.<br>Center |

|-------|------------|----------------------------------------------|--------------|-----------------|------------------|

| Right |            |                                              | 1            |                 |                  |

| 1     | VCC        | Supply voltage digital part, I/O, 4MHz-osc.  |              | 3392            | 193.8            |

| 2     | SG_D1      | Port 1 halfbridge D                          | N Open Drain | 3392            | 316              |

| 3     | SG_D2      | Port 2 halfbridge D                          | N Open Drain | 3392            | 431              |

| 4     | GND        | Ground                                       |              | 3392            | 546              |

| 5     | SG_C1      | Port 1 halfbridge C                          | N Open Drain | 3392            | 661              |

| 6     | SG_C2      | Port 2 halfbridge C                          | N Open Drain | 3392            | 776              |

| 7     | GND        | Ground                                       |              | 3392            | 891              |

| 8     | SG_B1      | Port 1 halfbridge B                          | N Open Drain | 3392            | 1006             |

| 9     | SG_B2      | Port 2 halfbridge B                          | N Open Drain | 3392            | 1121             |

| 10    | GND        | Ground                                       |              | 3392            | 1236             |

| 11    | SG_A1      | Port 1 halfbridge A                          | N Open Drain | 3392            | 1351             |

| 12    | SG_A2      | Port 2 halfbridge A                          | N Open Drain | 3392            | 1466             |

| 13    | GND        | Ground                                       |              | 3392            | 1581             |

| 14    | PSEP1      | Port 1 temperature measurement               | N Open Drain | 3392            | 1696             |

| 15    | PSEP2      | Port 2 temperature measurement               | N Open Drain | 3392            | 1811             |

| 16    | VCC        | Supply voltage digital part , I/O, 4MHz-osc. |              | 3392            | 1926             |

| 17    | MULT_I05   | Multi purpose I/O no. 5                      | Mult-IO      | 3392            | 2151             |

| Тор   |            |                                              |              |                 |                  |

| 18    | MULT_IO4   | Multi purpose I/O no. 4                      | Mult-IO      | 2862            | 2286             |

| 19    | GND        | Ground                                       |              | 2730            | 2286             |

| 20    | VCC_LOAD   | Power supply load output pins 1 and 2        |              | 2115            | 2286             |

| 21    | LOAD1      | Load output to measuring capacitor           | P Open Drain | 1976.6          | 2286             |

| 22    | LOAD2      | Load output to measuring capacitor           | P Open Drain | 1835            | 2286             |

| 23    | SPI_DO_IOO | Output serial SPI interface or IOO           | Mult-IO      | 1656.2          | 2286             |

| 24    | SPI_DI_I01 | Input serial SPI interface or IO1            | Mult-IO      | 1544.2          | 2286             |

| 25     | SPI_CLK_IO2                | Clock serial SPI interface or IO2                                            | Mult-IO                         | 1432.2 | 2286   |

|--------|----------------------------|------------------------------------------------------------------------------|---------------------------------|--------|--------|

| 26     | GND                        | Ground                                                                       |                                 | 1320.2 | 2286   |

| 27     | OSC_IN                     | Input to 4MHz ceramic resonator                                              |                                 | 1208.2 | 2286   |

| 28     | OSC_OUT                    | Output to 4MHz ceramic resonator                                             |                                 | 1096.2 | 2286   |

| 29     | VCC_OSC                    | 4MHz Oscillator supply voltage                                               |                                 | 984.2  | 2286   |

| 30     | SPI_CSN_RST<br>SPI_SSN_RST | Slave select or RST input (High active)                                      | Input with pull-down            | 872.2  | 2286   |

| 31     | SPI_ENA                    | Serial SPI interface enable                                                  |                                 | 760.2  | 2286   |

| 32     | MULT_IO3                   | Select for Wheatstone comparator MUX or Interrupt or Multi purpose I/O no. 3 | Wheatstone<br>select<br>Mult-IO | 648.2  | 2286   |

| 33     | GND                        | Ground                                                                       |                                 | 536.2  | 2286   |

| 34     | Vcc                        | Supply voltage digital part , I/O, 4MHz-osc.                                 |                                 | 424.2  | 2286   |

| Left   |                            | , ,,,,                                                                       |                                 |        |        |

| 35     | Vcc                        | Supply voltage digital part , I/O, 4MHz-osc.                                 |                                 | 83     | 2003.3 |

| 36     | Vcc-SENSE                  | Supply voltage SENSE pins                                                    |                                 | 83     | 1891.3 |

| 37     | SENSE_IN                   | Input internal CMOS comparator, connect to Vcc if not used                   | Analog In                       | 83     | 1779.3 |

| 38     | SENSE_OUT                  | Output internal CMOS comparator                                              | Analog Out                      | 83     | 1667.3 |

| 39     | UCOMP1                     | External comparator circuit connection                                       | Analog Out                      | 83     | 1555.3 |

| 40     | UCOMP2                     | External comparator circuit connection                                       | Analog Out                      | 83     | 1443.3 |

| 41     | STOP                       | Stop input measuring signal                                                  |                                 | 83     | 1331.3 |

| 42     | GND                        | Ground                                                                       |                                 | 83     | 1219.3 |

| 43     | VCC_LCD                    | Supply voltage LCD, 10kHz osc., bandgap                                      |                                 | 83     | 1045   |

| 44     | CPUMP1                     | LCD voltage doubling and stabilization                                       | Analog Out                      | 83     | 933    |

| 45     | CPUMP2                     | LCD voltage doubling and stabilization                                       | Analog Out                      | 83     | 821    |

| 46     | CPUMP3                     | LCD voltage doubling and stabilization                                       | Analog Out                      | 83     | 709    |

| 47     | LCD_COM1                   | LCD line driver for 1/2, 1/3, 1/4 duty                                       | LCD Buffer                      | 83     | 597    |

| 48     | LCD_COM2                   | LCD line driver for 1/2, 1/3, 1/4 duty                                       | LCD Buffer                      | 83     | 485    |

| 49     | LCD_COM3                   | LCD line driver for 1/3, 1/4 duty, row driver for 1/2 duty                   | LCD Buffer                      | 83     | 373    |

| 50     | GND                        | Ground                                                                       |                                 | 83     | 261    |

| 51     | LCD_COM4                   | LCD line driver for 1/4 duty, row driver for 1/2, 1/3 duty                   | LCD Buffer                      | 83     | 149    |

| Botton | n                          |                                                                              |                                 |        |        |

| 52     | LCD_SEG1                   | LCD row driver                                                               | LCD Buffer                      | 612.6  | 83     |

| 53     | LCD_SEG2                   | LCD row driver                                                               | LCD Buffer                      | 724.6  | 83     |

| 54     | LCD_SEG3                   | LCD row driver                                                               | LCD Buffer                      | 836.6  | 83     |

| 55     | LCD_SEG4                   | LCD row driver                                                               | LCD Buffer                      | 948.6  | 83     |

| 56     | LCD_SEG5                   | LCD row driver                                                               | LCD Buffer                      | 1060.6 | 83     |

| 57     | LCD_SEG6                   | LCD row driver                                                               | LCD Buffer                      | 1172.6 | 83     |

| 58     | LCD_SEG7                   | LCD row driver                                                               | LCD Buffer                      | 1347   | 83     |

| 59     | LCD_SEG8                   | LCD row driver                                                               | LCD Buffer                      | 1459   | 83     |

| 60     | LCD_SEG9                   | LCD row driver                                                               | LCD Buffer                      | 1571   | 83     |

| 61     | LCD_SEG10                  | LCD row driver                                                               | LCD Buffer                      | 1683   | 83     |

| 62     | LCD_SEG11                  | LCD row driver                                                               | LCD Buffer                      | 1795   | 83     |

| 63     | LCD_SEG12                  | LCD row driver                                                               | LCD Buffer                      | 1907   | 83     |

| 64     | LCD_SEG13                  | LCD row driver                                                               | LCD Buffer                      | 2019   | 83     |

| 65     | LCD_SEG14                  | LCD row driver                                                               | LCD Buffer                      | 2131   | 83     |

| 66     | GND                        | Ground                                                                       |                                 | 2928   | 83     |

# **Dimensions and Pad Opening**

The exact Die size is  $2.37 \times 3.47$  mm, the Wafer thickness  $725\mu m$ . The IC is expected to be used predominantly as Chip On Board (COB). Therefore it is essential to have a Pad Opening that is suitable for bonding machines:

Width: 90µm Height: 116µm

| Tak   | ole of Contents                                                    | Page |

|-------|--------------------------------------------------------------------|------|

| 3     | Converter Front End                                                | 3-2  |

| 3.1   | Overview                                                           | 3-2  |

| 3.2   | Measurement Principle                                              |      |

| 3.3   | Connecting the Strain Gauges                                       |      |

| 3.3.  |                                                                    |      |

| 3.3.  | 5                                                                  |      |

| 3.3.  | •                                                                  |      |

| 3.3.4 | ·                                                                  |      |

| 3.3.  |                                                                    |      |

| 3.3.  | -                                                                  |      |

| 3.3.  |                                                                    |      |

| 3.3.  |                                                                    |      |

| 3.4   | Capacitor, Cycle Time, Averaging                                   |      |

| 3.4.  |                                                                    |      |

| 3.4.  | -                                                                  |      |

| 3.4.  |                                                                    |      |

| 3.4.  | -                                                                  |      |

| 3.4.  |                                                                    |      |

| 3.4.0 |                                                                    |      |

| 3.5   | Modes and Timings                                                  | 3-15 |

| 3.5.  | •                                                                  |      |

| 3.5.  | 2 Single Conversion Mode                                           | 3-15 |

| 3.5.  | •                                                                  |      |

| 3.5.4 |                                                                    |      |

| 3.5.  |                                                                    |      |

| 3.5.0 | _                                                                  |      |

| 3.5.  |                                                                    |      |

| 3.5.  | 8 Temperature Measurement                                          | 3-23 |

| 3.6   | Post-processing                                                    | 3-25 |

| 3.6.  |                                                                    |      |

| 3.6.  | Compensation of Load Cell Gain & Offset Drift (Mult_TKG, Mult_TkO) | 3-26 |

| 3.6.  | •                                                                  |      |

| 3.6.4 | •                                                                  |      |

| 3.6.  | 5 Gain-Drift of PSØ81 itself - Optimization with Mult_PP           | 3-31 |

| 3.6.  | • –                                                                |      |

| 3.6.  | 7 Mult_UB - Power Supply Rejection                                 | 3-34 |

# 3 Converter Front End

#### 3.1 Overview

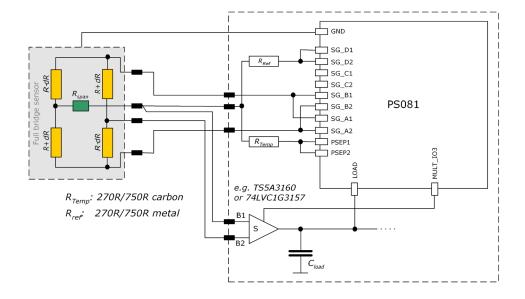

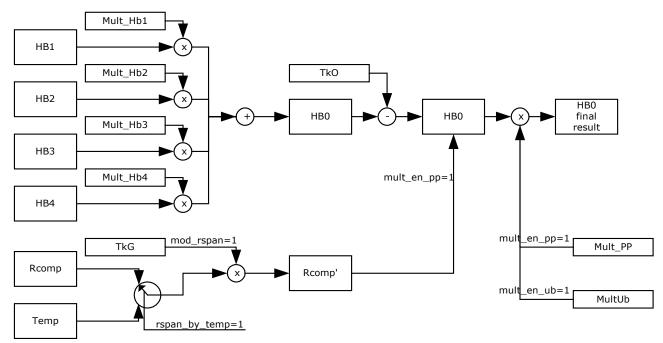

Figure 3.1 Overview

The PICOSTRAIN based converter has the strain gage ports (SG\_Ax to SG\_Dx) to measure:

- 4 independent half bridges (quattro mode)

- 2 half bridges that form a full bridge

- 2 independent half bridges

- 1 classical Wheatstone bridge

- 1 single half bridge

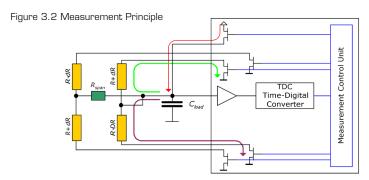

#### 3.2 Measurement Principle

The strain itself is measured by means of discharge time measurements. The discharge time is defined by the strain gauge resistance and the capacitor Cload. Both, the strain gage with positive change and the one with negative change are measured. The ratio of the two discharge times provides the strain information. The precision of the time measurement is done with about 15 ps resolution (0.5 ps with averaging).

This chapter will explain the components of the front-end, the parameters to set and how to dimension external components.

There are many ways to connect your strain gage sensor to PSØ81. In this section we show how to connect them.

# 3.3 Connecting the Strain Gauges

**Caution:** To get good results it is mandatory to connect the load cell body to GND of the electronic. A simple standard wire is sufficient.

#### 3.3.1 Half Bridge

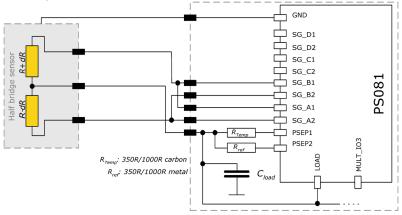

Figure 3.3 Connecting a half bridge

#### Note:

The half bridge is connected like a full bridge to get a better zero drift behavior. This requires the bridge setting = 1 (register 3, bridge[1:0] = 1)

The multiplication factors should have positive sign, e.g. Mult\_Hb1 = +1, Mult\_Hb2 = +1.

With this kind of connection the zero drift of the electronic is the same as in full bridge mode and deeply within OIML specification.

For maximum speed it may be helpful to connect the half bridge as a half bridge and not as a full bridge (register 3, bridge[1:0] = 0, pins SG\_A1 & SG\_A2 only). With AVRate = 2 the maximum speed is possible and up to 1 kHz can be reached. An additional systematic zero drift will occur which is nearly the same on all devices. The value of this zero drift is approx.  $\pm 6$  nV/V/K. This zero drift is a result of a longer bond wire on SG\_A2 compared to SG\_A1. The bond wire resistance is not compensated by the RDSON compensation of the chip. Therefore, this systematic drift can be compensated on the PCB by a longer wire on SG\_A1.

When using a standard PCB with cooper layers 35  $\mu$ m thick, the SG\_A1 trace on the PCB from the chip to the connecting pads of the load cell should be (t.b.d.) mm longer than the SG\_A2 trace (if a width of 8 mil is used). This compensation method is very reliable and stable an gives a zero drift behavior deeply within OIML specifications.

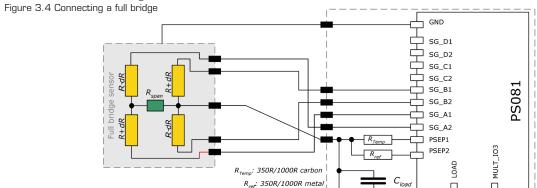

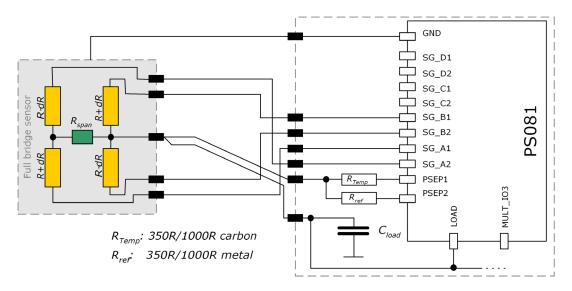

# 3.3.2 Full Bridge

#### Note:

This is the standard PICOSTRAIN bridge (a full bridge made of 2 half bridges with a single Rspan resistor optionally). The bridge setting is 1 (register 3, bridge[1:0] = 1).

The multiplication factors should have positive sign, e.g.  $Mult_{Hb1} = +1$ ,  $Mult_{Hb2} = +1$ . Therefore, it is necessary to follow exactly the wiring with respect to positive and negative strain.

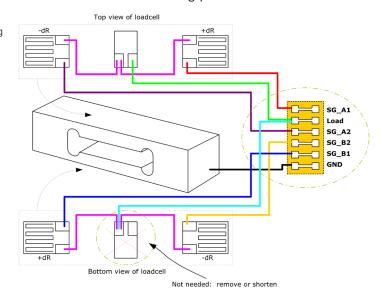

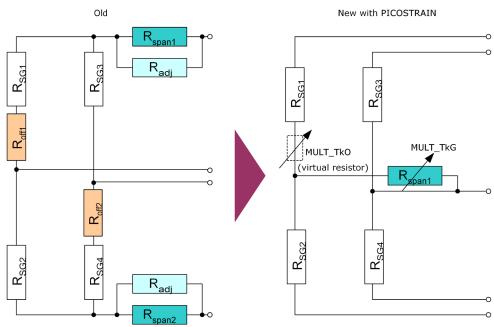

Existing sensors with Wheatstone bridge connection can be adopted easily by changing the wiring in the patch-field of the load cell as shown in the following picture:

Figure 3.5 Adapted load cell wiring

The advantage of the PICOSTRAIN full bridge compared with the Wheatstone bridge is a higher resolution of approximately 0.6 bits (factor 1.5 higher).

# 3.3.3 Full Bridge Parallel (zero drift optimized)

This mode is not recommended any longer (canceled in December 2009). Please see bug report (Section 7.1) for further details.

## 3.3.4 Full Bridge connected as Half Bridge (Current Saving Connection)

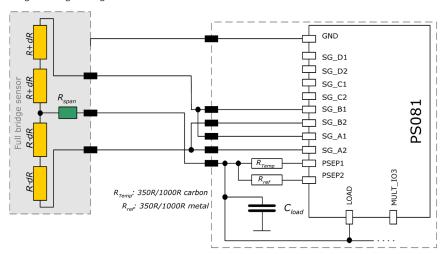

Figure 3.6 Current saving full bridge wiring

#### Note:

This wiring is suited if all strain gages are on the same site (top OR bottom) of the load cell. Then 2 strain gage resistors can be connected in series to get a 2 kOhm half bridge. This way, the current into the sensor is reduced by factor 2 and therefore this wiring is especially suited for minimum current e.g. solar driven applications.

The bridge setting is 1 (register 3, bridge[1:0] = 1).

The multiplication factors should have positive sign, e.g. Mult\_Hb1 = +1, Mult\_Hb2 = +1.

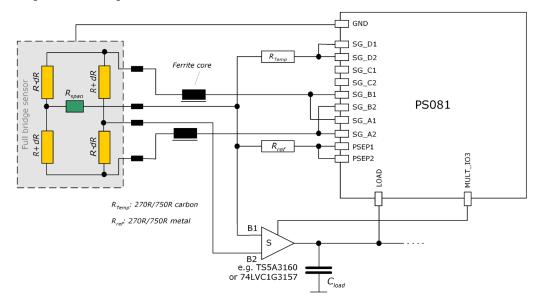

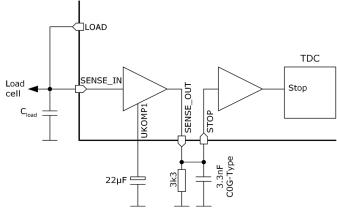

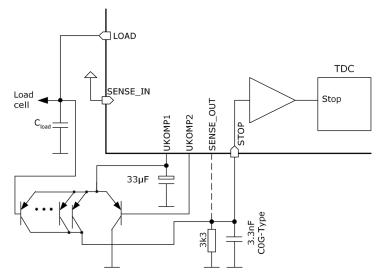

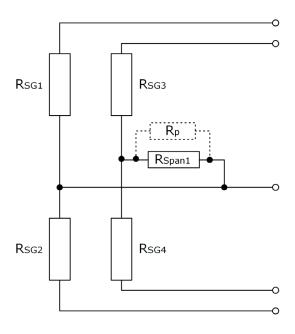

#### 3.3.5 Wheatstone Bridge

Figure 3.7 Connecting a Wheaston bridge

For Wheatstone bridges an additional external analog switch is needed. We recommend TS5A3160 because it has a good behavior even at supply voltages lower than 2.7 V. For supply voltages of 3.0 V or higher 74LVC1G3157 is a good choice, too.

#### Note:

In Wheatstone mode the system looses 0.6 bit of resolution. Because of this, Wheatstone connection is only recommended for applications with long wires (> 1 m) and for first tests if you don't want to modify your load cell wiring.

The bridge setting is 1 (register 3, bridge[1:0] = 1).

The multiplication factors must have opposite sign, e.g. Mult\_Hb1 = +1, Mult\_Hb2 = -1.

If the Wheatstone bridge has a gain compensation resistor (Rspan) the standard setting for TKGain is 0.75 (ConfigRegO8). The factor 0.75 doesn't modify the span compensation behavior of the load cell. In any case "Mod\_Rspan" has to be set to 1 (ConfigRegO1, Bit 6)

To avoid reflections in the Wheatstone bridge we do strongly recommend the use of ferrite cores. They are placed in the two lines which are connected directly to PSO81. Ordinary (SMD-)ferrite cores with a damping of 1000hm @ 100MHz with a low DC resistance (<0.10hm) can be used. As a consequence a lower offset drift and better EMI behavior can be expected.

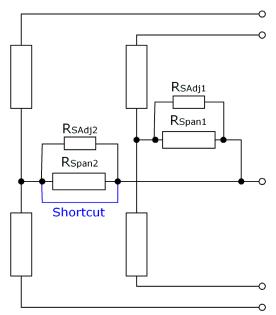

#### **Caution:**

Only Wheatstone bridges with one Rspan or without Rspan (uncompensated) can be used. PICOS-TRAIN cannot work properly with Wheatstone bridges that have two Rspan.

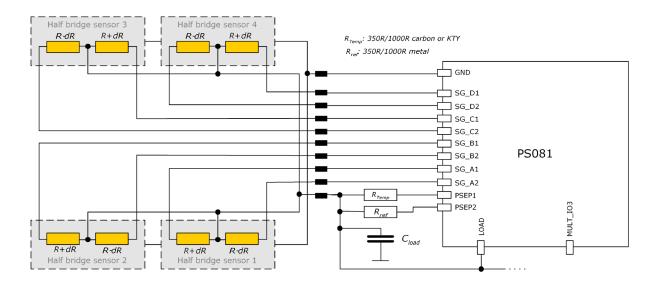

# 3.3.6 Quattro Bridge (4 sensors)

Figure 3.8 Connecting a quattro bridge

In some cases four sensors are used. Then, each half bridge is connected to one port. This is a typical connection e.g. for quattro body scales. The result of each half bridge can be read but also the overall result.

The bridge setting is 3 (register 3, bridge[1:0] = 3).

Each half bridge is assigned its own multiplication factor. This allows to trim the gain of the four load cells just by software. All multiplication factors should have positive sign, e.g.  $Mult_{B0} = +1$ ,  $Mult_{B0} = +1$ ,  $Mult_{B0} = +1$ ,  $Mult_{B0} = +1$ .

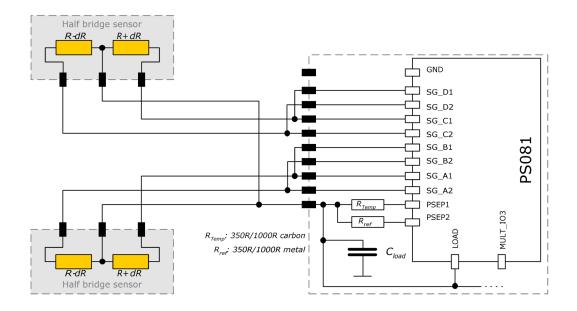

# 3.3.7 2 Half Bridges separately

Figure 3.9 Connecting 2 separate half bridges

#### Note:

Normally, two half bridges are wired as full bridge (one result). Nevertheless, sometimes the result of the half bridge is of interest and the two half bridges shall be measured separately. In this case, the two half bridges can be connected in the quattro mode as shown in the picture above and so the results can be read separately. Connecting this way guarantees that the results are gain-compensated. The result of each half bridge can be calculated then as follows:

$$HB1 = (A-B) / 2$$

and  $HB2 = (C-D) / 2$ .

If you want to read 2 half bridges separately but with a low offset drift, please connect like suggested in ,Full bridge' and contact the acam team for further steps.

The bridge setting is 3 (register 3, bridge[1:0] = 3).

All multiplication factors should have positive sign, e.g. Mult\_Hb1 = +1, Mult\_Hb2 = +1,

$Mult_Hb3 = +1$ ,  $Mult_Hb4 = +1$ .

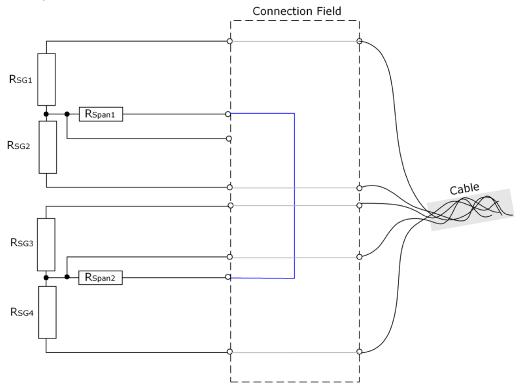

# 3.3.8 6-wire Technology

PSO81 may be connected to the load cell also in 6-wire technology. Figures 3.11 and 3.12 show the wiring. 6-wire technology is used to compensate the resistance of the sensor cable. With PSO81 the cable resistance is compensated as part of the comparator gain compensation (Mult\_PP, see also section 3.6.2).

Figure 3.10 6-wire technology with PICOSTRAIN wiring

Figure 3.11 6-wire technology with Wheatstone wiring

3-9

# 3.4 Capacitor, Cycle Time, Averaging

# 3.4.1 Load Capacitor (Cload)

The load capacitor is an important part of the circuit and has direct influence on the quality of the measurement and the temperature stability. Therefore, we recommend the following values and materials:

```

Rsg = 350R → Cload = 300nF to 400nF

Rsg = 1000R → Cload = 100nF to 150nF

```

Cload can be calculated by =  $0.7 \times Rsg \times Cload \approx 100 \, \mu s - 150 \, \mu s$

# Recommended materials:

- COG\* for highest accuracy

- CFCAP good, but not as good as COG

- X7R with some minor losses in temperature stability

- Polyester with some minor losses in temperature stability

We do not recommend the use of ZOG capacitors!

#### Note:

COG capacitors are definitely the best choice for high end applications (e.g. 6000 divisions (or higher) legal-for-trade scales). CFCAP are also a good choice for high end scales and legal-for-trade scales. For consumer scales X7R are the first choice because of their low cost. But they introduce additional gain drift at lower temperatures ( < +5 °C ).

For consumer applications also a lot of other capacitors are well suited (e.g. Polyester).

#### 3.4.2 Cycle Time (cytime)

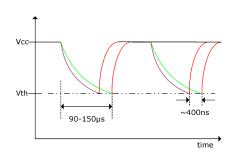

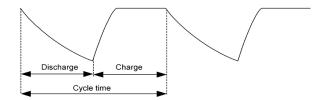

The cycle time is the time interval between subsequent discharge time measurements. It covers the discharge time and the time to charge again Cload. Following figure illustrates this relation.

Figure 3.12 Cycle time

<sup>\*</sup> COG capacitor up to 100nF are available by Murata GRM31 series

<sup>\*\*</sup> Multi layer ceramic capacitor from Taiyo Yuden

The discharge time is given by the value of the strain gage resistor and the given capacitor Cload. The recommended discharge time is in the range of 80 to 150 µs (at 3.3V). The charge time has to be long enough to provide a full recharge of Cload and is typically 30% of the cycle time. If the cycle time is set too small (in the range of the discharge time or smaller) an overflow will occur.

The cycle time is set in register 2, cytime[13:4]. The cycle time is normally generated by the high speed clock and can be set in steps of 2  $\mu$ s. The only exception is the "Stretched Mode" (see chapter ,Modes' 3.5) where the cycle time is generated by the internal 10 kHz oscillator and therefore configurable in steps of 100  $\mu$ s.

#### Example:

cytime[13:4] = 80  $\rightarrow$  80 x 2  $\mu$ s = 160  $\mu$ s cycle time in all modes except stretched mode cytime[13:4] = 10  $\rightarrow$  10 x 100  $\mu$ s = 1 ms cycle time in stretched mode

The recommended minimum cycle time setting is 1.4 times the discharge time. E.g. 140  $\mu$ s if the discharge time is 100  $\mu$ s.

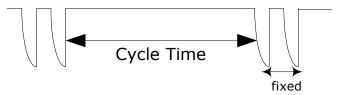

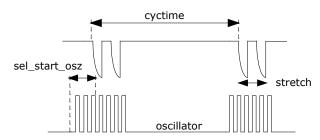

#### 3.4.3 Cycle Time in Stretched Mode

In stretched mode the parameter cyclime has a special function. In this case, it does NOT define the time of discharging + charging, instead it defines the time between 2 discharging cycles in multiples of  $100 \, \mu s$ :

Figure 3.13: Cycle time in streched mode

There are several parameters to adjust in stretched mode. Please have a look at Stretched Mode settings in section 3.5.3.

# 3.4.4 Averaging (avrate)

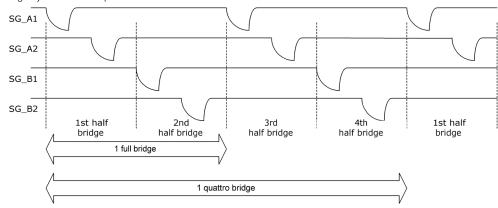

The number of strain gages respectively half bridges connected defines how many discharging cycles are needed to make one complete ratio measurement:

Half bridge  $\rightarrow$  2 cycles Full bridge  $\rightarrow$  4 cycles Quattro bridge  $\rightarrow$  8 cycles

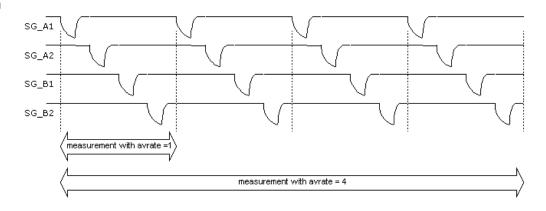

Figure 3.14 Discharge cycles for a complete measurement

Those numbers of cycles for each mode together define 1 sample (avrate=1). This is also the minimum needed for one complete ratio measurement.

### 3.4.5 Better resolution by averaging

In PSO81, the resolution can be increased by internal averaging. The sample size of the averaging is specified by parameter avrate in register 2. The standard deviation of the result will be improved by nearly the square root of the sample size. The following picture shows the correlation for a full bridge:

Figure 3.15 Averaging

One sequence in this example is made of 4 samples, each made of 4 discharge cycles. So in total 1 measurement takes 16 discharge cycles.

Besides the discharging cycles given by the sample there are additional measurements like gain compensation or fake measurements for better stability. All those measurements together form in total then a measurement sequence. In other words, a sequence contains all measurements needed to get the final result. It also defines the total conversion time. For more details on conversion time please see the chapters ,Conversion Time' 3.5.5 and ,Modes' 3.5.

Of course, the sample size of averaging dominates the update rate. While the resolution is improved by a factor  $1/\sqrt{\text{avrate}}$ , the maximum update rate is reduced by the factor avrate.

```

sample size (avrate) \nearrow \rightarrow Resolution \nearrow \rightarrow Max. update rate \searrow

```

Also the lowest possible current consumption is influenced by the sample size. It grows by a factor avrate.

sample size (avrate)  $\nearrow$   $\rightarrow$  Minimum current  $\nearrow$

Recommendation: We strongly recommend not to use avrate = 1. In principle it works but the drift significantly increases and it can be used only for low end resolution applications. The recommended minimum sample size is avrate = 2. It is also not recommended to use odd numbers at lower avrate up to 50. E.g., do not use avrate = 7, use instead avrate = 8 or avrate = 6.

**Important:** At low avrates (<= 32) the factor psO81adjust (Configreg\_O3, Bit [9:4]) should be set to 2x avrate. Example: avrate = 8 -> set psO81adjust to 16

### 3.4.6 Resolution and Converter Precision

In this document the terms resolution and converter precision are often used in the same context, however, there is a difference in their meaning:

- Resolution: refers to the digital value which can be displayed (or resolved) within the chip. This is basically the HBO register in a 24-bit format, where the MSB is indicating a negative number (two's complement). Expressed in numbers the result can be shown from -8388608 (0x800000) to +8388607 (0x7FFFFF). One LSB has thereby the valency of 10nV/V (2mV/V divided by 200,000). Example: at 3V the valency of 1 LSB is 10nV/V x 3V = 30nV.

- Converter Precision (sometimes also referred to as "accuracy"): this is the accuracy given by the converter, normally defined by the standard deviation or RMS (root mean square) noise. The value of the precision is normally given in effective number of bits (ENOB). With PSO81 an RMS

noise as low as 10nV at 3.3V can be achieved, or expressed in ENOB up to 19.5 Bits (related to 2mV/V). An overview of the converter precision at different update rates is given in several tables in section 2.4. However, a rough estimation can be done by the equations given in the following.

The base converter precision for a half bridge at avrate = 1 (only for calculation purposes, not recommended to be used) and a recommended discharge time of 90 to 150  $\mu$ s in fast settling mode and 2 mV/V excitation is:

With internal comparator: 13.3 Bit eff. With external bipolar comparator: 13.8 Bit eff.

At higher values of avrate[] the resolution is calculated as:

$$ENOB = ENOB[AVRate = 1] + \frac{\ln(\sqrt{AVRate * Bridgefactor})}{\ln(2)}$$

The Bridge-factor is: 2 for full bridges

4 for quattro bridges

#### Example 1:

avrate = 12, Quattro bridge, internal comparator

ENOB =  $13.3 + \ln(\sqrt{12*4})/\ln(2) = 13.3 + 2.8 = 16.1$  Bit eff. = 70,000 effective divisions =

10,000 peak-peak divisions in fast settle mode (without SINC-filter).

#### Example 2:

avrate = 450, Full bridge, external comparator

ENOB =  $13.8 + \ln (\sqrt{450*2})/\ln(2) = 13.8 + 4.9 = 18.7$  Bit eff. = 425,000 effective divisions =

70,000 peak-peak divisions in fast settle mode (without SINC filter).

### Example 3:

avrate = 100, Full bridge, external comparator, expressed in nV RMS

ENOB =  $13.8 + \ln (\sqrt{100 \times 2}) / \ln(2) = 13.8 + 3.8 = 17.6$  Bit eff.

2^17.6 = 198,700 eff. divisions with a 2mV/V sensor operated at 3V

$\rightarrow$  3V x 2mV/V = 6000µV divided by 198,700 = 30.2nV RMS

Note: The effective number of bits (ENOB) in the equation are related to 2mV/V sensitivity of the sensor. If the sensitivity is different with your sensor, the result needs to be corrected by the reduction in sensitivity. E.g.: you calculate 18.7 bit with the equation, but your sensor has only 1mV/V

instead of 2mV/V. Then this corresponds to a reduction by factor 2, which is 1-bit, so the ENOB is 17.7 bit in this case.

The effective resolution (ENOB) is also reduced when Wheatstone connection is used instead of PICOSTRAIN connection. The reason for that is the reduction of the strain by 1/3 because when discharging over 1 strain gage of the bridge the other 3 strain gages are in parallel and lower the extension/strain of the gage to measure. Expressed in ENOB the reduction is -0.6 bit.

# 3.5 Modes and Timings

The PSO81 has 3 basic operating modes as well as combinations of them. They are related to the sampling frequency and the active time of the 4 MHz oscillator. Therefore, the selection has influence on the stability of the result and the current consumption.

The basic modes are:

- Continuous Mode

- Single Conversion Mode

- Stretched Mode

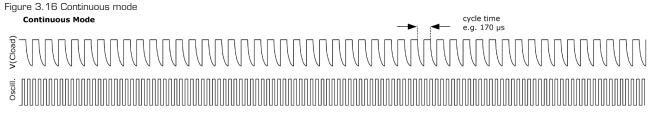

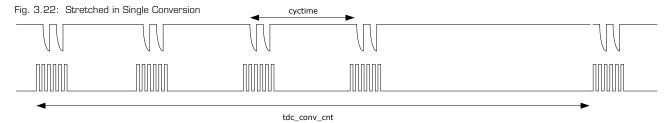

# 3.5.1 Continuous Mode

The chip is making continuously discharge time measurements. The oscillator is on all the time. This mode is the choice for applications targeting highest resolution. It is the standard mode for all applications that allow a current consumption  $> 500 \, \mu A$ .

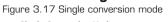

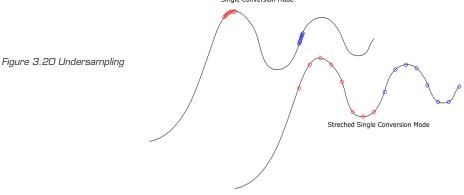

#### 3.5.2 Single Conversion Mode

The chip makes a complete measurement sequence and then goes to sleep mode. The oscillator is

on only for the sequence. This mode offers the lowest current consumption and is best choice for body scales.

Pure Single Conversion Mode should be used only in mechanically stable systems like body scales, because it implies undersampling. The consequence of undersampling is that mechanical oscillations of the weighing system will end up in unstable data.

#### 3.5.3 Stretched Mode

Streched Mode combines the advantage of a few measurements (to save current) and a reasonable distribution of these measurements for avoiding undersampling. Hence, the discharge cycles are stretched in a way that the total number is not increased but the distribution is improved.

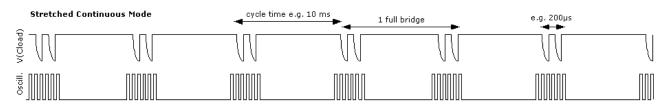

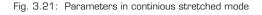

#### 3.5.3.1 Stretched Continuous Mode

Figure 3.18 Stretched continuous mode

Stretched Conitnuous Mode combines stretched mode and continuous mode. There are longer intervals between the discharge time measurements for the half bridges. The oscillator is activated only for each half bridge measurement.

This mode is used in applications that target high resolution at low current ( $< 500 \,\mu\text{A}$ ). It also has a good frequency response (e.g. load cell vibrations) on the input signal. The response can easily be calculated by the Nyquist theorem. This mode together with a good software anti-vibration filter gives best vibration suppression at lowest current. This mode is recommended e.g. for battery driven solar kitchen scales.

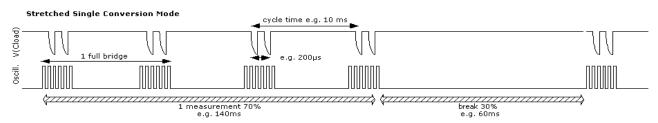

## 3.5.3.2 Stretched Single Conversion Mode

Figure 3.19 Stretched single conversion mode

For mechanically sensitive weigh scales like kitchen scales the PSO81 provides the stretched mode combined with the single conversion mode. In this mode the two resistors of a half bridge are measured subsequently, but the next pair of discharge time measurements follows delayed. Therefore, the sample points of a single sequence can cover minimum a full period of the mechanical oscillation. Thanks to the integration of the samples within one sequence the result will normally be stable if the break is <30% of the time.

Again, the oscillator is switched on only for each discharge time measurement. But, as the oscillator needs some time to reach the full amplitude, the total active time of the oscillator is longer than for pure Single Conversion Mode. The current consumption in stretched single conversion mode is therefore a little bit increased compared to the single conversion mode.

#### Four major parameters define the operation mode:

single\_conversion: Selects between continuous operation and single separated measurements.

Selects between 4 MHz oscillator continuously running while measuring and running the oscillator only for the duration of 1 or 2 discharge cycles (recom

mended 2 discharge cycles)

cycletime: Defines the time interval between single or pairs of discharge cycles. It is

based on the 4 MHz clock or in stretched mode on the 10 kHz clock.

avrate: Sample size of averaging. Defines the number of complete ratio measure

ments that make a single measurement sequence (internal averaging).

## single\_conversion / continuous

Configuration: Register 2, Bit 2: single\_conversion

single\_conversion = 0 Selects continuous mode. In this mode the PSØ81 is continuously

measuring. The 4 MHz oscillator is on continuously. This takes about

130 μA @ 3.0 V.

single\_conversion = 1 Selects single conversion mode. In this mode the PSØ81 makes one

complete measurement and then switches off the 4 MHz oscillator for

the duration of the single conversion counter.

stretch

Configuration: Register 3, Bits 12, 13: stretch

stretch = 0 off

stretch = 1 The 4 MHz oscillator is on only for the duration of a single discharge time measure

ment. The cycle time (time between subsequent discharge time measurements) is

calculated on the basis of the 10 kHz oscillator.

- not recommended -

stretch = 2 or 3 The 4 MHz oscillator is on only for the duration of a single half bridge measure-

ment (two discharge time measurements). The cycle time (time between subsequent half bridge time measurements) is calculated on the basis of the 10 kHz oscillator. The time interval between the two discharge time measurement for a

halfbridge is 200 µs in case stretch = 2 or 300 µs in case stretch = 3

#### Stretched Mode Settings

In stretched mode there are several parameters which configure the mode, these are:

stretch[13:12] in Configreg\_O3

cytime[13:4] in Configreg\_02

sel\_start\_osz[19:17] in Configreg\_O3

single\_conversion [2] in Configreg\_O2

tdc\_conv\_cnt[23:16] in Configreg\_OO

Those parameters set the stretch mode. The

following 2 pictures show how the parameters are applied, one showing the continious stretched the

other the single conversion stretched mode.

The cyclime-parameter defines the time waited for the next discharging. By the parameter stretch, the time between 2 discharging cycles can be defined. The parameter sel\_start\_osz defines what time the oscillator is started before the discharging cycles are coming.

Basically in Single Conversion Stretched mode the parameters remain the same. But tdc\_conv\_cnt defines additionally the time between measurement sequences.

#### 3.5.4 Mode Selection Criteria

Table 3.1 Mode Selection criteria

| Applications                 | Mo         | de         | Parameters            | Description                   |  |

|------------------------------|------------|------------|-----------------------|-------------------------------|--|

| Highest resolution with no   |            | Continuous | single_conversion = 0 | Continuously measuring,       |  |

| current limitation           |            | mode       | stretch = 0           | 4 MHz oscillator on all the   |  |

| Standard mode for all ap-    | Continuous |            |                       | time                          |  |

| plications with > 500 µA     | ıtin       |            |                       |                               |  |

| current capability           | Ö          |            |                       |                               |  |

| High resolution but lower    | \          | Stretched  | single_conversion = 0 | Continuously measuring. 4     |  |

| current                      | Stretched  | continuous | stretch = 2 or 3      | MHz oscillator on only during |  |

|                              | etc        | mode       | cycle time =          | the discharge time measure-   |  |

|                              | ξŢ         |            | cytime*100µs          | ment.                         |  |

| Lowest current consumption   |            | Single     | single_conversion = 1 | option with lowest current    |  |

| Mechanically stable applica- |            | conversion | stretch = 0           | consumption, undersampling    |  |

| tions like pressure sensors  |            | mode       |                       | -> no suppression of me-      |  |

|                              |            |            |                       | chanical vibrations           |  |

| High resolution but low cur- | ion        | Stretched  | single_conversion = 0 | option with low current con-  |  |

| rent,                        | /ers       | mode       | stretch = 2           | sumption and oversampling     |  |

| e.g. battery driven legal-   | conversion |            | cycle time =          | for suppression of mechani-   |  |

| for-trade scales with 3000   |            |            | cytime*100µs          | cal vibrations.               |  |

| divisions                    | Single     |            |                       |                               |  |

| High resolution but lowest   | \          | Stretched  | single_conversion = 1 | option with very low current  |  |

| current,                     | hed        | single     | stretch = 2 or 3      | consumption and overs-        |  |

| e.g. solar scales            | Stretched  | conversion | cycle time =          | ampling for suppression of    |  |

|                              | St         | mode       | cytime*100µs          | mechanical vibrations.        |  |

# 3.5.5 Conversion Time / Measuring Rate (Continuous Mode)

The time for one complete measurement can be calculated by means of following formula:

Tconversion = CycleTime\*(2\*avrate \* Bridge-factor + 6 +MFake\*2 + 1)

Mfake = #Fake measurements, Temperature measurement on

| Mfake-Register | #Fake Measurements | Note:                                    |

|----------------|--------------------|------------------------------------------|

| 0              | 0                  | Fake measurements are necessary          |

| 1              | 2                  | to avoid that the next measurement       |

| 2              | 4                  | starts while the ALU is still processing |

| 3              | 16                 | data from the former measurement.        |

Example1: Cycle time = 110 µs

AVRate =12

Quattro bridge

Mfake = 1

Tourision = 110  $\mu$ s\*(2\*12\*4 + 6 + 2 + 1) =11.55 ms

The maximum measuring rate is 86.6 Hz

Example2: Cycle time = 110 µs

AVRate = 450 Full bridge Mfake = 2

Tourision = 110  $\mu s*(2*450*2+6+4+1)$  =199.21 ms

The maximum measuring rate is 5.02 Hz

#### 3.5.6 Conversion Time / Measuring Rate (Single Conversion Mode)

If PSØ81 is configured to run in Single Conversion Mode (Bit 4 in configreg\_02), the measuring rate is defined by the value in tdc\_conv\_cnt[23:16] in configreg\_00. This value corresponds directly to the conversion time (multiplied by 6.4ms).

# Example:

```

configreg_O0: Ox158200 \rightarrow tdc\_conv\_cnt[23:16] = Ox15 = 21 decimal

\rightarrow 21 \times 6.4 ms = 0.1344 second